- 您现在的位置:买卖IC网 > Sheet目录3878 > PIC18F4610T-I/ML (Microchip Technology)IC MCU FLASH 32KX16 44QFN

2003 Microchip Technology Inc.

DS39582B-page 183

PIC16F87XA

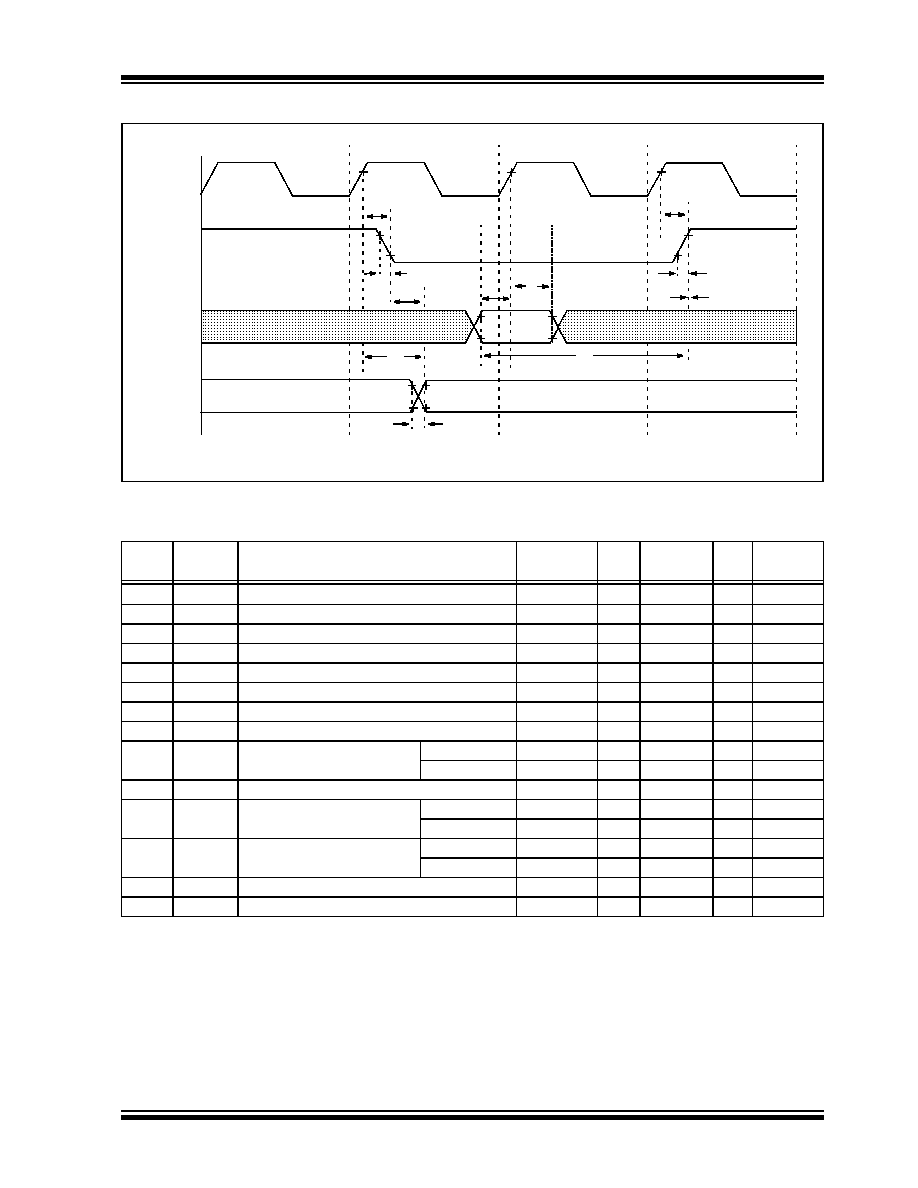

FIGURE 17-5:

CLKO AND I/O TIMING

TABLE 17-4:

CLKO AND I/O TIMING REQUIREMENTS

Note: Refer to Figure 17-3 for load conditions.

OSC1

CLKO

I/O pin

(Input)

I/O pin

(Output)

Q4

Q1

Q2

Q3

10

13

14

17

20, 21

19

18

15

11

12

16

Old Value

New Value

Param

No.

Symbol

Characteristic

Min

Typ

Max

Units Conditions

10*

TOSH2CKLOSC1

↑ to CLKO ↓

—

75

200

ns

(Note 1)

11*

TOSH2CKHOSC1

↑ to CLKO ↑

—

75

200

ns

(Note 1)

12*

TCKR

CLKO Rise Time

—

35

100

ns

(Note 1)

13*

TCKF

CLKO Fall Time

—

35

100

ns

(Note 1)

14*

TCKL2IOVCLKO

↓ to Port Out Valid

—

0.5 TCY + 20

ns

(Note 1)

15*

TIOV2CKH

Port In Valid before CLKO

↑

TOSC + 200

—

ns

(Note 1)

16*

TCKH2IOI

Port In Hold after CLKO

↑

0—

—

ns

(Note 1)

17*

TOSH2IOVOSC1

↑ (Q1 cycle) to Port Out Valid

—

100

255

ns

18*

TOSH2IOIOSC1

↑ (Q2 cycle) to Port Input

Invalid (I/O in hold time)

Standard (F)

100

—

ns

Extended (LF)

200

—

ns

19*

TIOV2OSH Port Input Valid to OSC1

↑ (I/O in setup time)

0

—

ns

20*

TIOR

Port Output Rise Time

Standard (F)

—

10

40

ns

Extended (LF)

—

145

ns

21*

TIOF

Port Output Fall Time

Standard (F)

—

10

40

ns

Extended (LF)

—

145

ns

22*

TINP

INT pin High or Low Time

TCY

——

ns

23*

TRBP

RB7:RB4 Change INT High or Low Time

TCY

——

ns

*

These parameters are characterized but not tested.

Data in “Typ” column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are

not tested.

These parameters are asynchronous events not related to any internal clock edges.

Note

1:

Measurements are taken in RC mode where CLKO output is 4 x TOSC.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F4610-E/PT

IC MCU FLASH 32KX16 44TQFP

PIC18F4610-E/ML

IC MCU FLASH 32KX16 44QFN

PIC18LF2331T-I/SO

IC MCU FLASH 4KX16 28SOIC

PIC18F4515T-I/PT

IC MCU FLASH 24KX16 44TQFP

PIC18F4431T-I/ML

IC MCU FLASH 8KX16 44QFN

PIC18F4431-E/ML

IC MCU FLASH 8KX16 44QFN

PIC18F4410T-I/ML

IC MCU FLASH 8KX16 44QFN

PIC18F4410-E/PT

IC MCU FLASH 8KX16 44TQFP

相关代理商/技术参数

PIC18F4610T-I/PT

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620-E/ML

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620-E/P

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620-E/PT

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620-E/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC18F 40MHZ TQFP-44 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC18F, 40MHZ, TQFP-44

PIC18F4620-I/ML

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620-I/P

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620-I/P

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F4620 DIP40